Concevoir les puces de demain grâce aux FPGA*s, une « glaise électronique » re-modelable a volonté, nous explique Bruno Levy. Bruno est Directeur de Recherche Inria au sein du projet ParMA de l’Inria Saclay et du Laboratoires de Mathématiques d’Orsay. Il conduit des recherches en physique numérique et en cosmologie. Il joue également le rôle d’ambassadeur pour Risc-V. Pierre Paradinas.

(*) FPGA : Pour « Field Programmable Gate Array », à savoir, ensemble de portes logiques programmable « sur le terrain » …

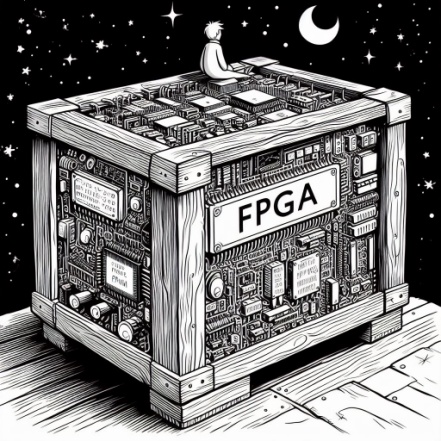

« S’il te plait, dessine moi la super-puce du futur pour l’IA de demain ? »

« Ça, c’est la caisse, la super-puce que tu veux est dedans ! » (D’après St Exupéry et Igor Carron)

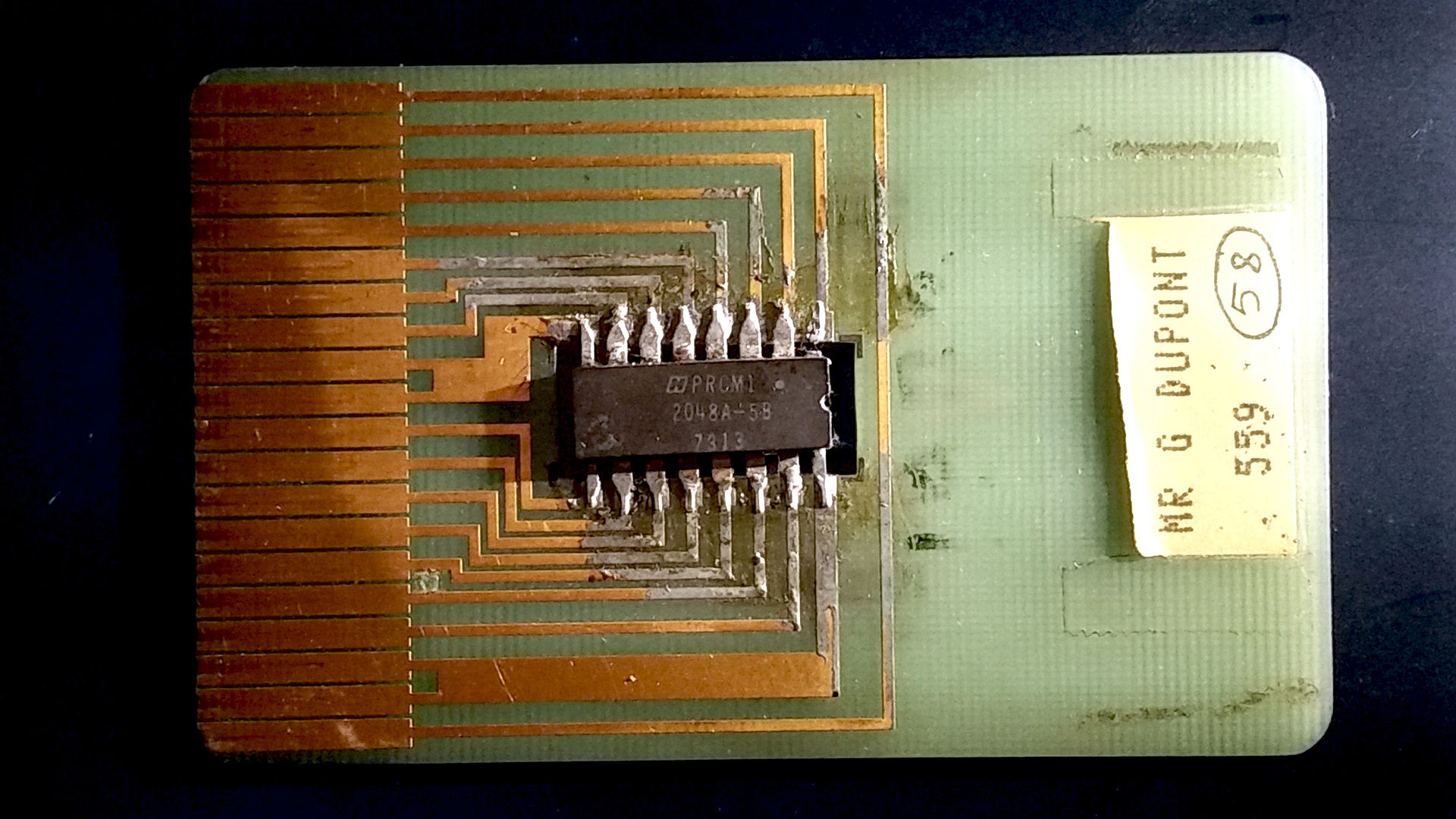

La micro-electronique : des milliards de connexions sans s’emmêler les fils ! Les circuits intégrés, ou « puces », sont d’incroyables réalisations technologiques. Ils ont été inventés en 1958 par Jack Kilby dans l’objectif de simplifier la fabrication des circuits électroniques. Cette industrie était alors confrontée au problème d’arriver à fabriquer de manière fiable un grand nombre d’éléments. Le plus gros problème était posé par le nombre considérables de fils censés connecter les composants entre eux ! En gravant directement par un procédé photographique les composants et leurs connexions dans un morceau de semi-conducteur de quelques millimètres carrés, son invention révolutionne ce domaine, car elle a permis non-seulement d’automatiser le processus de fabrication, mais également de miniaturiser la taille des circuits et leur consommation énergétique de manière spectaculaire. Grâce à son invention, il propose une dizaine d’années plus tard, en 1972, la première calculatrice de poche. Dans la même période (en 1971), la firme Intel, à présent bien connue, sort une puce révolutionnaire, le Intel 4004, qui contient un ordinateur quasi complet (le tout premier microprocesseur), également dans l’objectif de fabriquer des calculatrices de poches. En quelques décennies, cette technologie progresse plus rapidement que n’importe quelle autre. Les premières puces des années 70 comportaient quelques milliers d’éléments (des transistors), connectés par des fils de quelques micromètres d’épaisseur (dans un millimètre on casait 1000 fils, ce qui était déjà considérable, mais attendez la suite…). Les puces d’aujourd’hui les plus performances comportent des centaines de milliards de transistors, et les fils font quelques nanomètres de large (dans un millimètre, on case maintenant un million de fils).

Comment fabrique-t-on une puce ? Il y a un petit problème : arriver à structurer la matière à l’échelle atomique ne peut pas se faire dans un garage ! Pour donner une idée de la finesse de gravure (quelques nanomètres), on peut garder à l’esprit que la lumière visible a une longueur d’onde entre 300 et 500 nanomètres. Autrement dit, dans l’intervalle minuscule correspondant à une seule longueur d’onde électromagnétique de lumière visible, on sait graver une centaine de fils !!! Alors avec quoi peut-on réaliser ce tour de force ? Toujours avec des ondes électromagnétiques, mais de très très petite longueur d’onde, émises par un laser, à savoir des ultra-violets très énergétiques (qui sont une forme de « lumière » invisible), appelés EUV pour Extreme Ultra Violets. La firme néerlandaise ASML maîtrise cette technologie et équipe les principaux fabricants de puces (appelés des « fondeurs »), dont le Taïwanais TSMC, Samsung et Intel, avec sa machine (à plusieurs centaines de millions d’Euros, grosse comme un autobus, bourrée de technologie) qui permet de graver la matière à l’échelle atomique . La machine, et surtout l’usine autour de celle-ci, coûtent ensemble plusieurs dizaines de milliards d’Euros ! A moins d’être elle-même un fondeur (comme Intel), une entreprise conceptrice de puces va donc en général dépendre de l’une de ces entreprises, qui a déjà réalisé les investissements colossaux, et qui va fabriquer les puces à partir de son design. Cela a été le cas par exemple de Nvidia (qui fabrique à présent la plupart des puces pour l’IA), qui a fait fabriquer ses trois premières générations de puces graphiques dans la fin des années 1990 par le fondeur Franco-Italien ST-Microelectronics (qui gravait alors en 500 nanomètres, puis 350 nanomètres), pour passer ensuite au Taïwanais TSMC, qui avait déjà à l’époque un processus plus performant.

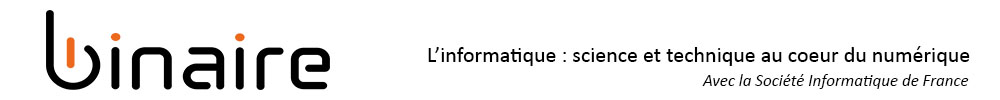

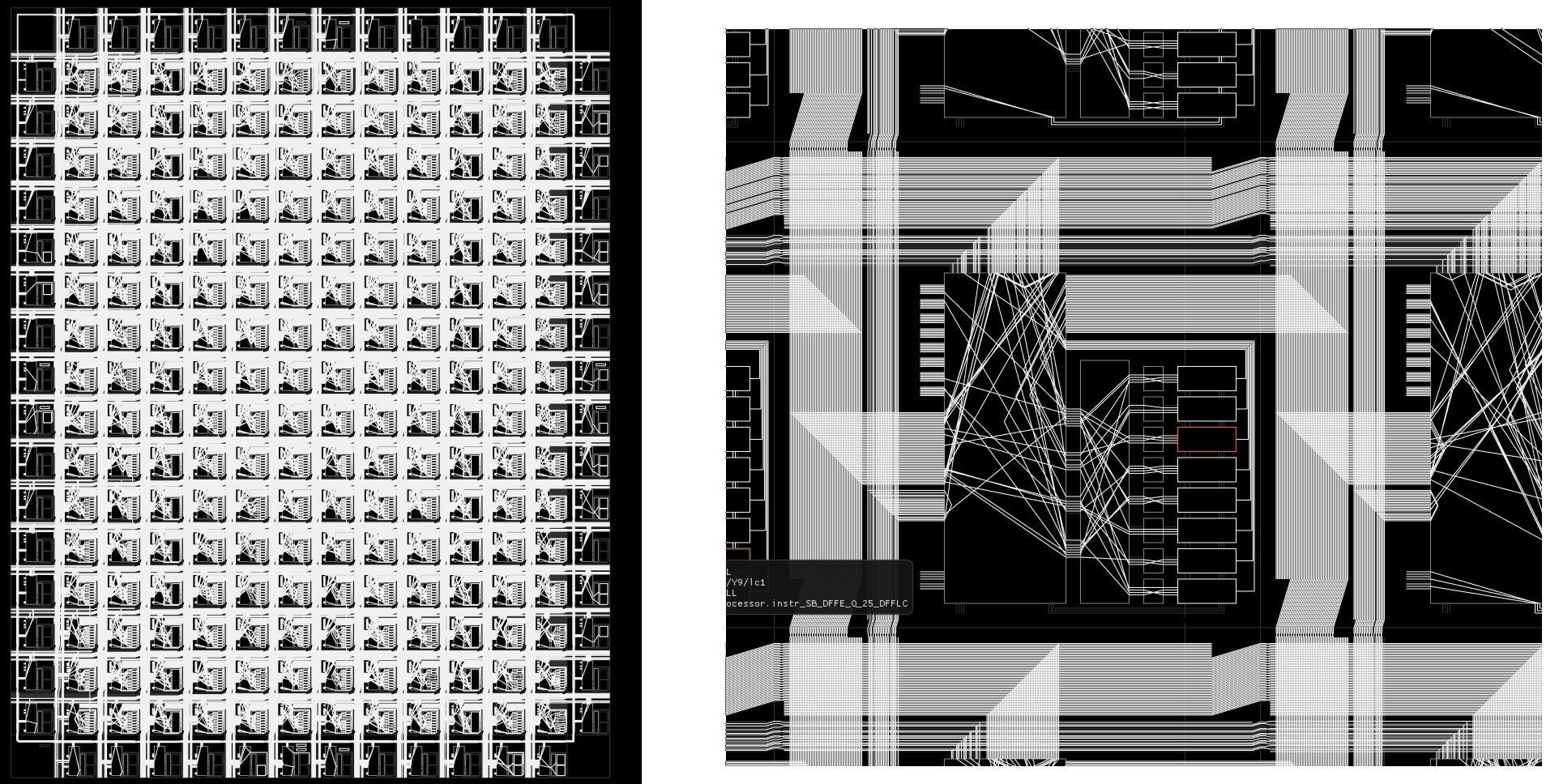

Représentation de l’intérieur d’un FPGA, constitué d’un grand nombre de portes logiques, de cellules de mémoire et d’aiguillages permettant de les connecter. Ici, le circuit correspond à FemtoRV, un petit processeur Risc-V conçu par l’auteur.

Et les petits acteurs ? Comment un petit acteur concepteur de puces peut-il accéder à cette technologie ? Le coût en faisant appel à un fondeur reste important, car pour chaque puce plusieurs étapes de développement sont à réaliser, comme la création des masques, sortes de « négatifs photo » permettant de créer par projection les circuits sur la puce. Afin de réaliser des prototypes, ou encore quand les exigences de performances sont moins importantes, il serait bien d’avoir une sorte de « boite » remplie de portes logiques, de fils et de cellules mémoires (comme sur l’illustration sous le titre), et de pouvoir rebrancher à volonté tous ces éléments au gré de l’imagination du concepteur. C’est exactement ce que permet de réaliser un FPGA. Un tel FPGA se présente sous la forme d’un circuit intégré, avec à l’intérieur tous ces éléments génériques, et un très grand nombre d’ « aiguillages » reconfigurables par logiciel (voir la figure). On peut le considérer comme une « glaise électronique », modelable à façon, permettant de réaliser n’importe quel circuit logique, à l’aide de langages de description spécialisés.

Il existe une grande variété de FPGA, des plus petits, à quelques dizaines d’Euros, comportant quelques milliers d’éléments logiques, jusqu’au plus gros, à plusieurs milliers d’Euros, comportant des millions d’éléments. Ceci rend le « ticket d’entrée » bien moins onéreux. Combinées avec la disponibilité de FPGAs à faible coût, deux autres nouveautés favorisent considérablement l’émergence de petits acteurs dans ce domaine :

- tout d’abord, l’apparition d’outils Open-Source, tels que Yosys et NextPNR, qui remplacent de grosses suites logicielles monolithiques par un ensemble d’outils simples, faciles à utiliser et réactifs. Ceci rend cette technologie accessible non-seulement aux petits acteurs, mais également à toute une communauté de hobbyistes, de manière similaire à ce qui s’est passé pour l’impression 3D.

- d’autre part, le standard ouvert RiscV fournit à tous ces projets une norme libre de droit, facilitant l’émergence d’un écosystème de composants compatibles entre eux (c.f. cet article sur binaire ). Il est assez facile de réaliser un processeur Risc-V à partir d’un FPGA (tutoriel réalisé par l’auteur ici ).

- et enfin, des initiatives comme TinyTapeOut, qui permettent à tout un chacun de s’initier à la fabrication de circuit intégrés, en intégrant les projets de plusieurs personnes sur une seule puce afin de réduire les coûts de production.

Pourquoi est-ce intéressant et qu’est-ce que ça change ? Au-delà d’introduire plus de « bio-diversité » dans un domaine jusqu’à présent dominé par quelques acteurs, certains domaines peuvent grandement bénéficier de la possibilité de créer facilement des circuits électroniques : par exemple, les expériences réalisées à l’aide de l’accélérateur à particules LHC (Large Hadron Collider) du CERN génèrent un très grand volume de données, qui nécessite une électronique spécialisée pour leur traitement. D’autres domaines d’application nécessitent de contrôler très exactement le temps, d’une manière telle que seule un circuit spécialisé peut le faire. Enfin, un grand nombre de gadgets de type « Internet des Objets » possède à l’intérieur un système informatique complet, tournant sous Linux, ce qui représente un ensemble de problèmes en termes de sécurité informatique. Ceci est résumé dans cet article qui décrit un scénario fictif, où des brosses à dents connectés sont utilisées pour organiser une attaque par déni de service. Même si ce scénario était fictif, il reste malheureusement très réaliste ! Grâce aux FPGAs, il sera possible de remplacer tous ces petits ordinateurs génériques de l’Internet des objets par des versions spécialisées, à la fois plus économes en énergie et moins sensibles aux attaques informatiques.

Et demain, une convergence entre le soft et le hard ? Avec les FPGAs, on assiste à une évolution où la frontière entre le soft (le logiciel) et le hard (le matériel) est de plus en plus ténue. Si on imagine qu’elle devienne totalement poreuse, on voit alors des ordinateurs qui reconfigurent automatiquement leurs circuits en fonction du programme à exécuter, afin d’être plus efficace et/ou de consommer moins d’énergie. Intel et AMD explorent déjà cette voie, en intégrant un FPGA dans un microprocesseur, ce qui permet de définir pour ce dernier de nouvelles instructions à volonté. En extrapolant encore plus loin cette vision, on pourra imaginer dans un futur proche une grande variété de schémas de conceptions et de modèles d’exécution, permettant de remplacer la puissance brute de calcul par plus de créativité et d’intelligence, réelle ou artificielle !

Alors, de quoi rêvent les FPGAs … ?

… de moutons électriques, bien évidement !

Bruno Lévy, Inria

Binaire a demandé à Bruno Levy, de nous parler d’un processeur spécifique le RISC-V. Ce processeur ouvert/libre pourrait rebattre les cartes des coeurs de processeurs. Bruno Levy est chercheur Inria, spécialiste des optimisations mathématiques, il a rejoint la nouvelle équipe projet PARMA (une machine mathématique à remonter le temps pour explorer l’univers). Bruno est aussi l’un des

Binaire a demandé à Bruno Levy, de nous parler d’un processeur spécifique le RISC-V. Ce processeur ouvert/libre pourrait rebattre les cartes des coeurs de processeurs. Bruno Levy est chercheur Inria, spécialiste des optimisations mathématiques, il a rejoint la nouvelle équipe projet PARMA (une machine mathématique à remonter le temps pour explorer l’univers). Bruno est aussi l’un des